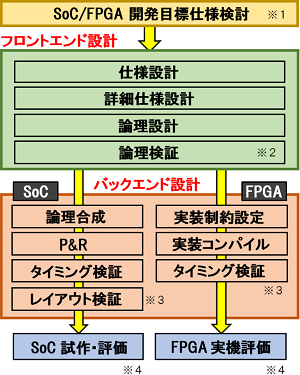

マイコン設計技術、高速インタフェース設計技術、画像処理、解析技術をベースにしたSoC設計サービスを提供します。また、汎用品で不足している機能、性能を補うためのFPGAによる設計サービスを提供します。

部分設計への対応が可能です。

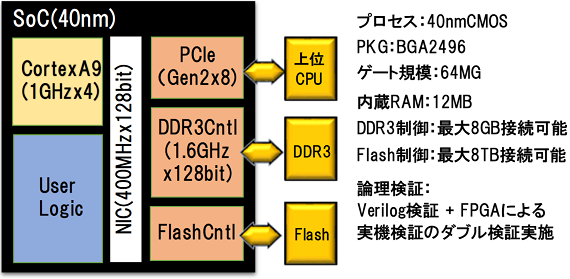

| マルチCPU搭載 SoC設計技術 |

|

|---|---|

| PCI制御設計技術 |

|

| Ethernet、CAN、USB 制御設計技術 |

|

| CPUシステムバス 制御技術 |

|

| DDRメモリ 制御設計技術 |

|

| 画像処理、解析技術 |

|

| 高位設計技術 |

|

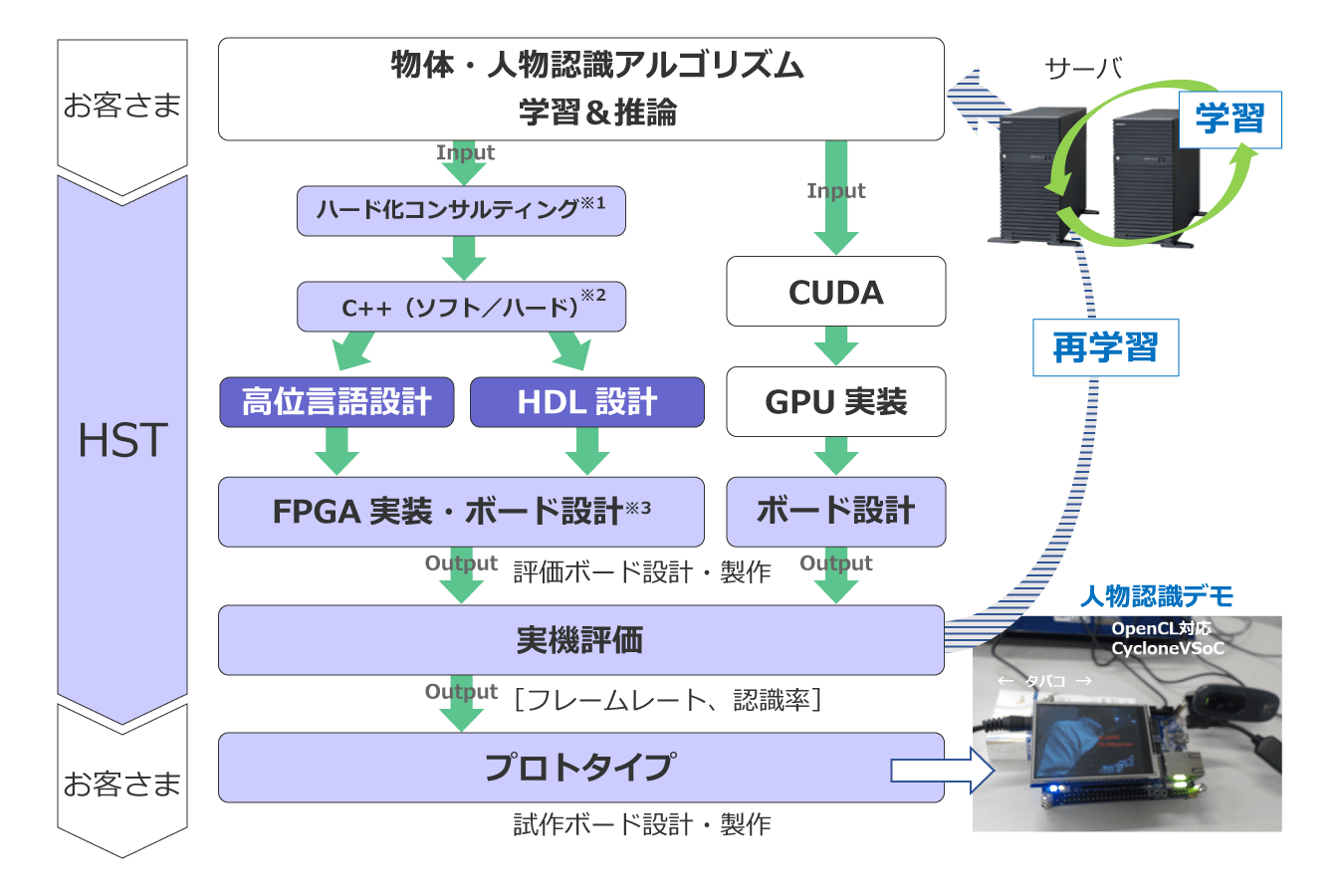

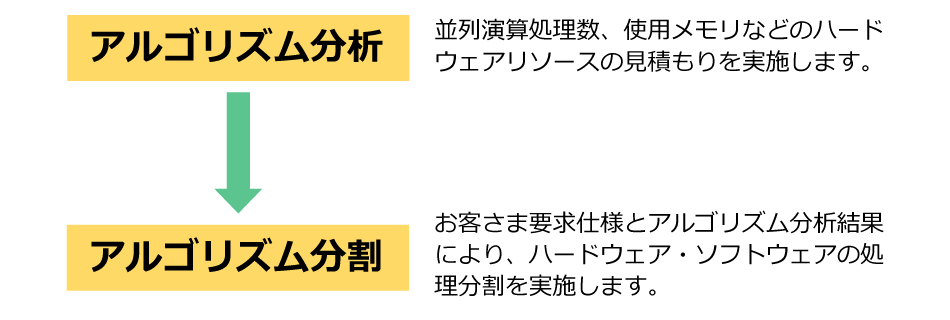

優れた半導体設計技術をFPGA設計に適用したデザインサービスを提供します。AI技術も加えて画像認識装置などを最適なFPGAで実現するソリューションを提案します。有力ベンダの先端FPGAの使いこなしを支援します。

コンサルティングから設計、実機評価までのワンストップ開発を実現します。作業の一部を切り出しての対応も可能です。

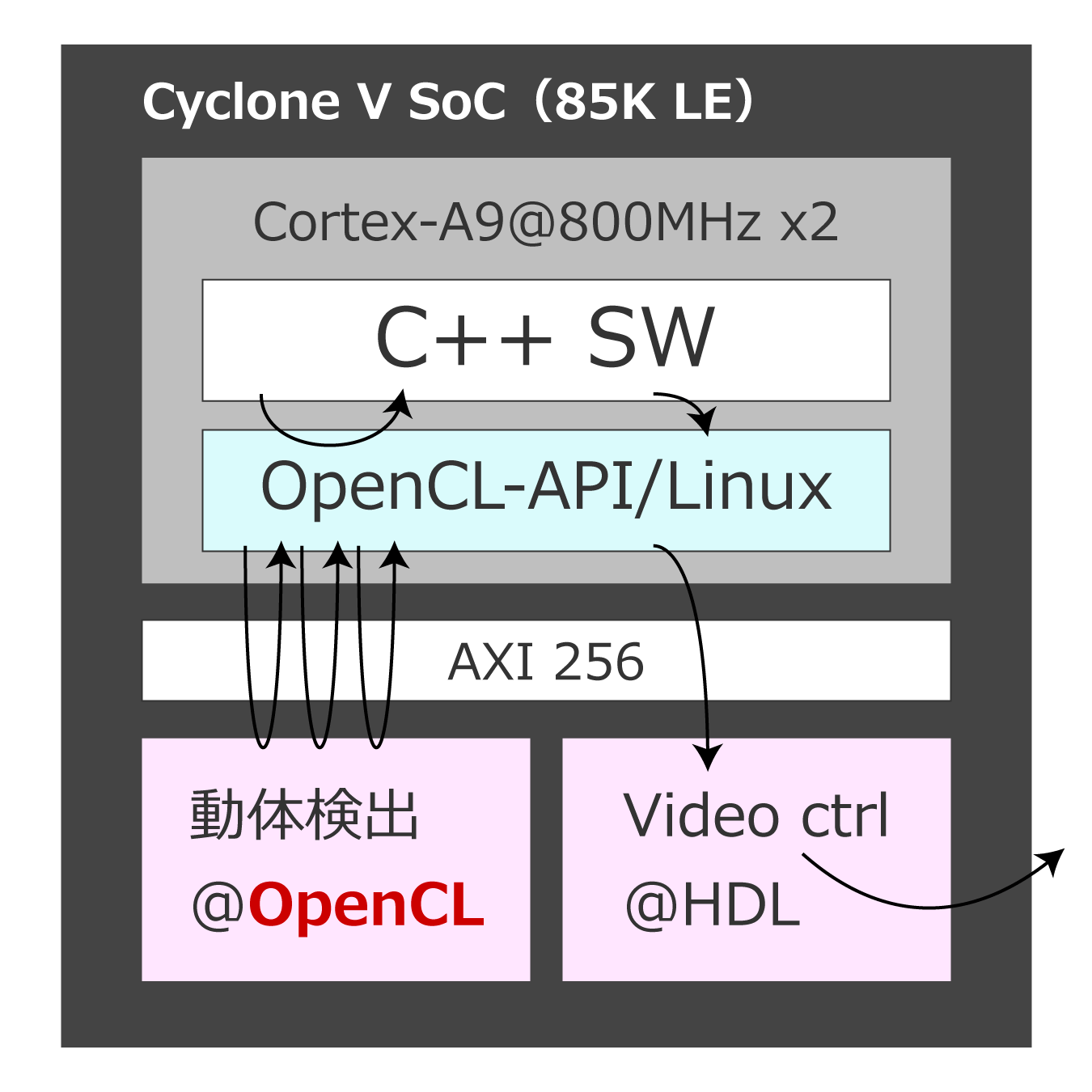

USBカメラ入力から、人物を認識して検知して表示装置に出力している様子

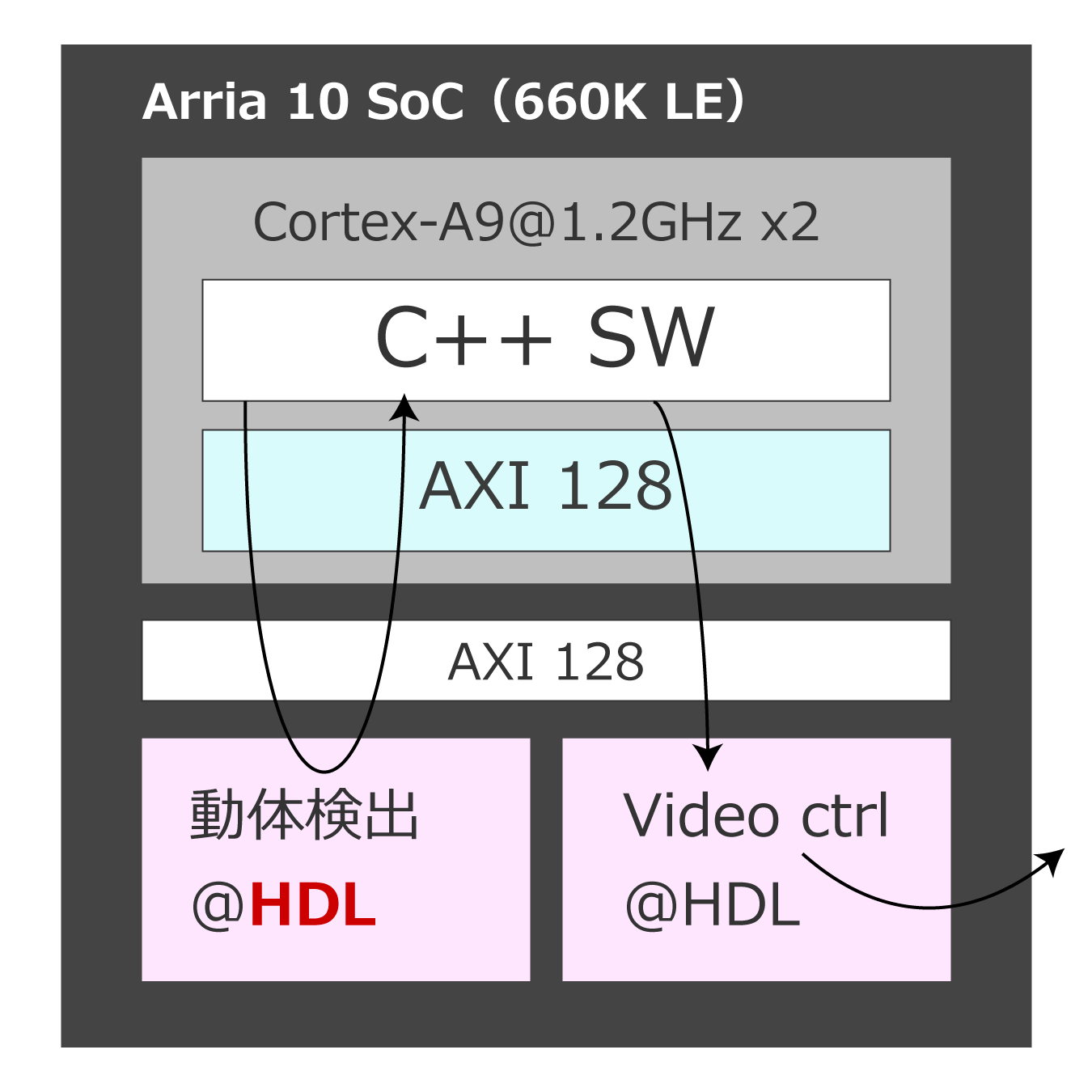

動体検出回路の構成最適化によりデータムーバの時間も低減

ボトル、椅子、人物を認識している様子

| Neural Net | Input Size | Precision | Device(FPGA) | Frame late |

|---|---|---|---|---|

| Segnet | 640×480 | FP16 | Stratix 10 | 〜2 fps |

| AlexNet(reduced) | 256×256 | INT32 | Zynq Ultrascale+ | 〜50 fps |

| Faster-RCNN | 320×256 | INT16 | Stratix 10 | 〜30 fps |

| Tiny YOLO | 352×288 | bfloat16 | Arria 10 | 〜60 fps |

当社は、Intel FPGAのパートナープログラムであるデザイン・ソリューション・ネットワークのメンバです。製品ロードマップ、ボード、IP、製品プロモーションへの早期アクセスや優先的な技術支援と販売支援といった、顧客サポートを加速させるIntel社の特典を利用し、最新技術でFPGA開発を行います。